VCXO Oscillator成為時(shí)鐘發(fā)生器的記錄隨筆

來源:http://www.kaikei-kansa.com 作者:金洛鑫電子 2019年08月05

時(shí)鐘發(fā)生器(CLK)與振蕩器有些類似,都是產(chǎn)生并提供產(chǎn)品時(shí)鐘信號(hào)的電子元器件,但是跟晶體振蕩器有很大的不同,晶振是一種頻率控制元器件,是依靠頻率振蕩后產(chǎn)生信號(hào)的,時(shí)鐘發(fā)生器則是在主板啟動(dòng)時(shí)提供初始化時(shí)鐘信號(hào),二者還是有比較明顯的區(qū)別.那么標(biāo)題中說到,VCXO晶振作為CLK時(shí)鐘發(fā)生器都是怎樣操作的呢?VCXO(壓控晶體振蕩器)是一種振蕩器,其頻率由晶體決定,但可以通過改變控制電壓進(jìn)行少量調(diào)節(jié).VCXO時(shí)鐘(CLK)發(fā)生器已經(jīng)用于各種應(yīng)用,例如數(shù)字電視,數(shù)字音頻,ADSL和STB.本應(yīng)用筆記提供了VCXO CLK發(fā)生器的一般結(jié)構(gòu),關(guān)鍵性能測(cè)量,PCB設(shè)計(jì)指南以及MAX 9485的測(cè)試設(shè)置,MAX9485是用于MPEG2和AC-3音頻應(yīng)用的VCXO CLKGen芯片.

VCXO CLK發(fā)生器的結(jié)構(gòu)與應(yīng)用

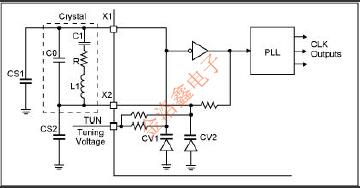

VCXO或壓控晶體振蕩器以晶體確定的頻率振蕩,但可通過控制電壓在較窄的范圍內(nèi)調(diào)節(jié),通常在0V-2V或0V-3V的范圍內(nèi).VCXO的調(diào)諧范圍約為±100ppm至±200ppm.圖1顯示了典型VCXO CLK發(fā)生器的結(jié)構(gòu)和晶體的電路模型.

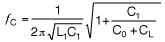

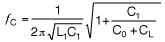

其中CL是等效負(fù)載電容,是CV1,2和CS1,2的集總和.更準(zhǔn)確地說,CL=(CV1+CS1)||(CV2+CS2).采用一階近似并考慮到C1<

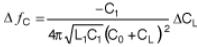

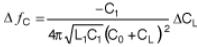

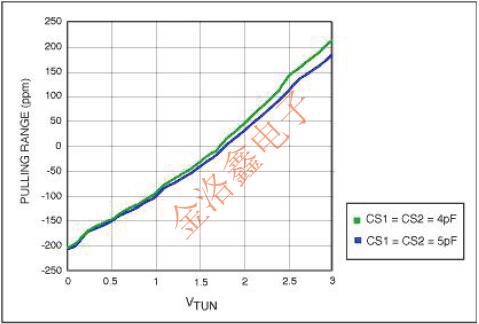

圖2顯示了fC在CS1值方面的典型曲線,其中CS1=CS2.

圖2.VCXO頻率與分流電容器CS1(CS1=CS2).

使用這種微調(diào)功能,通常將VCXO和PLL組合在一起,以創(chuàng)建具有微調(diào)功能的CLK發(fā)生器.VCXO CLK發(fā)生器已用于各種應(yīng)用,例如數(shù)字電視,數(shù)字音頻,ADSL和STB.Maxim的MAX9485是一款CLK發(fā)生器芯片,專為MPEG-2和Dolby Digital音頻(AC-3)應(yīng)用而設(shè)計(jì)[1].它可以提供幾乎所有用于音頻數(shù)模轉(zhuǎn)換器的頻率.它支持從12kHz到96kHz的采樣頻率.Maxim還在為其他應(yīng)用開發(fā)VCXO CLK發(fā)生器.

VCXO CLK發(fā)生器的關(guān)鍵參數(shù)

有許多參數(shù)來表征VCXO CLK發(fā)生器.最重要的是調(diào)諧電壓范圍,中心頻率,拉動(dòng)(調(diào)諧)范圍和輸出CLK的抖動(dòng).調(diào)諧電壓范圍是VCXO石英晶振控制電壓的變化范圍.該電壓控制變?nèi)荻O管的電容.通常它在0V-2V或3V的范圍內(nèi).中心頻率是VCXO輸出頻率范圍中間的頻率.牽引范圍是上(或下)頻率變化與中心頻率的比率.該比率通常以ppm(百萬分率)表示.該測(cè)量提供VCXO的相對(duì)牽引范圍.通常,拉伸范圍約為100ppm-200ppm,這取決于VCXO和所選晶體的結(jié)構(gòu).CLK抖動(dòng)是CLK發(fā)生器的關(guān)鍵測(cè)量.有幾種抖動(dòng)定義.兩種最常用的抖動(dòng)測(cè)量稱為周期抖動(dòng)和周期到周期抖動(dòng).我們將在第4節(jié)中討論它們.抖動(dòng)取決于CLK發(fā)生器的結(jié)構(gòu),它隨芯片而變化,對(duì)CLK發(fā)生器的抖動(dòng)要求也因應(yīng)用而異.

晶體選擇和電路板設(shè)計(jì)

VCXO CLK發(fā)生器的質(zhì)量和特性會(huì)受到晶體選擇和PCB布局的影響.在晶體選擇方面,除頻率,封裝,精度和工作溫度范圍外,對(duì)于VCXO應(yīng)用,用戶必須注意等效串聯(lián)電阻和負(fù)載電容.串聯(lián)電阻提供晶體的功耗測(cè)量.電阻值越小,振蕩器啟動(dòng)越容易.負(fù)載電容是晶體的重要參數(shù).首先,它決定了晶體的共振頻率.通常,晶體的標(biāo)記頻率意味著在將指定的負(fù)載電容與其并聯(lián)連接之后晶體的諧振頻率.大號(hào)等于規(guī)定的負(fù)載電容,但這不是將值從1/(2π√L1Ç1).因此,很明顯VCXO的調(diào)諧范圍與CL的值密切相關(guān).對(duì)于較小的負(fù)載電容值,VCXO調(diào)諧范圍限制在上側(cè);同樣,較大的電容值會(huì)降低下側(cè)的調(diào)諧范圍.加載電容的正確值取決于VCXO的特性.

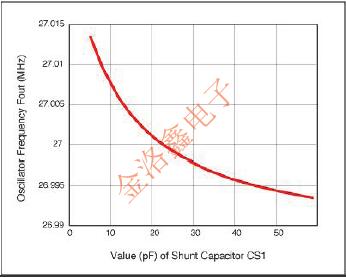

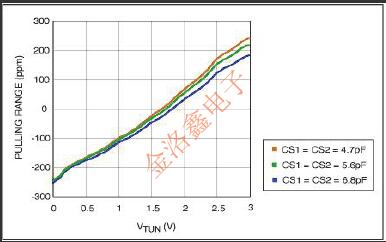

例如,在MAX9485設(shè)計(jì)中,為了平衡調(diào)諧范圍,調(diào)諧曲線的中心和電路板設(shè)計(jì)的簡(jiǎn)易性,我們選擇了Ecliptek(ECX-5527-27)[2]的具有14pf負(fù)載電容的27MHz晶振.有了這樣的晶體,MAX9485可以提供±200ppm的脈沖范圍,參見圖3.應(yīng)該提到的是,晶體的拉伸范圍也隨包裝而變化.通常,金屬罐裝封裝具有比表面安裝器件(SMD)更大的拉動(dòng)范圍.然而,最近DAISHINKUCorp[5]制造了一種新的SMD晶體,可提供與金屬罐裝晶體相似的拉伸范圍.我們測(cè)試了SMD晶振(DSX530GA),發(fā)現(xiàn)兩個(gè)4pf并聯(lián)電容的調(diào)諧范圍約為±200ppm,見圖4.

圖4

為了限制VCXO的調(diào)諧范圍,我們可以通過改變外部并聯(lián)電容來設(shè)置上限.并聯(lián)電容的值在4ps-7ps的范圍內(nèi),具體取決于電路板的寄生電容.另一方面,較低的范圍由內(nèi)部矢量的值確定,其不能在外部改變.為了減少寄生電容對(duì)上調(diào)諧范圍的影響,在電路板布局中,我們應(yīng)該盡量減小晶體引腳對(duì)地的寄生電容,從而在引腳與接地和電源方案之間提供良好的間隙.有關(guān)電路板布局的詳細(xì)信息,請(qǐng)參考MAX9485評(píng)估(EV)套件[4].

測(cè)量輸出CLK抖動(dòng)的設(shè)置

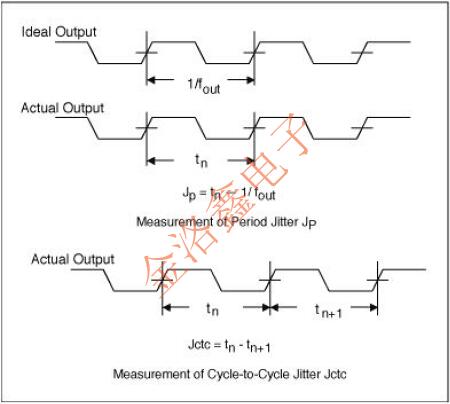

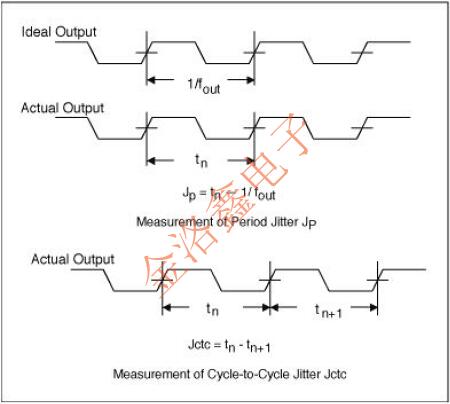

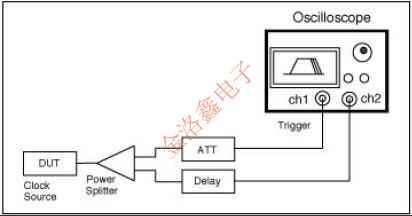

對(duì)于石英晶體振蕩器,抖動(dòng)是一項(xiàng)重要的性能測(cè)量.有兩種最常用的抖動(dòng)定義:周期抖動(dòng)和周期間抖動(dòng),見圖5細(xì)節(jié).為了測(cè)量抖動(dòng),我們可以使用高速數(shù)字采樣示波器對(duì)大量數(shù)據(jù)進(jìn)行采樣,并根據(jù)定義計(jì)算抖動(dòng).Tektronix(TDS7254)或Lecroy(Wavepro960)的示波器使用配備的軟件提供這些測(cè)量.我們還可以使用高速數(shù)字示波器來測(cè)量時(shí)域中的周期抖動(dòng)[3].圖5顯示了設(shè)置.通過時(shí)域方法,我們無法測(cè)量周期到周期的抖動(dòng).但是,如果每個(gè)周期的抖動(dòng)噪聲是獨(dú)立且相同分布的,則周期間抖動(dòng)是周期抖動(dòng)的1.414倍.MAX9485可根據(jù)不同的音頻采樣頻率和頻率比例因子產(chǎn)生21種不同的輸出頻率.我們使用了圖6中所示的設(shè)置測(cè)量所有可能的輸出CLK頻率的周期抖動(dòng).表1顯示了測(cè)量結(jié)果.

圖5.輸出抖動(dòng)測(cè)量.

從該表中我們可以看出,通常Oscillator頻率越高,抖動(dòng)越低.但是,如果我們使用相對(duì)度量來描述抖動(dòng),例如單位間隔(UI),從表格的最后一列看,抖動(dòng)是可比較的.另外,注意到36.864MHz,33.8688MHz,24.5760MHz和12.288MHz的頻率可以通過不同的采樣頻率Fs和比例因子產(chǎn)生,這導(dǎo)致不同的抖動(dòng)測(cè)量.因此,當(dāng)使用這些頻率時(shí),用戶應(yīng)選擇Fs和產(chǎn)生最低抖動(dòng)的比例因子.

VCXO CLK發(fā)生器的結(jié)構(gòu)與應(yīng)用

VCXO或壓控晶體振蕩器以晶體確定的頻率振蕩,但可通過控制電壓在較窄的范圍內(nèi)調(diào)節(jié),通常在0V-2V或0V-3V的范圍內(nèi).VCXO的調(diào)諧范圍約為±100ppm至±200ppm.圖1顯示了典型VCXO CLK發(fā)生器的結(jié)構(gòu)和晶體的電路模型.

圖1.典型VCXO CLK發(fā)生器的框圖.

隨著變?nèi)荻O管CV1和CV2的電容變化,晶振的模型受到影響,振蕩頻率也會(huì)發(fā)生變化.兩個(gè)分流外部并聯(lián)電容器CS1和CS2用于調(diào)節(jié)調(diào)諧范圍并偏移中心頻率.數(shù)學(xué)上,根據(jù)圖1中的晶體電路,晶體的共振頻率可表示為

其中CL是等效負(fù)載電容,是CV1,2和CS1,2的集總和.更準(zhǔn)確地說,CL=(CV1+CS1)||(CV2+CS2).采用一階近似并考慮到C1<

圖2顯示了fC在CS1值方面的典型曲線,其中CS1=CS2.

圖2.VCXO頻率與分流電容器CS1(CS1=CS2).

VCXO CLK發(fā)生器的關(guān)鍵參數(shù)

有許多參數(shù)來表征VCXO CLK發(fā)生器.最重要的是調(diào)諧電壓范圍,中心頻率,拉動(dòng)(調(diào)諧)范圍和輸出CLK的抖動(dòng).調(diào)諧電壓范圍是VCXO石英晶振控制電壓的變化范圍.該電壓控制變?nèi)荻O管的電容.通常它在0V-2V或3V的范圍內(nèi).中心頻率是VCXO輸出頻率范圍中間的頻率.牽引范圍是上(或下)頻率變化與中心頻率的比率.該比率通常以ppm(百萬分率)表示.該測(cè)量提供VCXO的相對(duì)牽引范圍.通常,拉伸范圍約為100ppm-200ppm,這取決于VCXO和所選晶體的結(jié)構(gòu).CLK抖動(dòng)是CLK發(fā)生器的關(guān)鍵測(cè)量.有幾種抖動(dòng)定義.兩種最常用的抖動(dòng)測(cè)量稱為周期抖動(dòng)和周期到周期抖動(dòng).我們將在第4節(jié)中討論它們.抖動(dòng)取決于CLK發(fā)生器的結(jié)構(gòu),它隨芯片而變化,對(duì)CLK發(fā)生器的抖動(dòng)要求也因應(yīng)用而異.

晶體選擇和電路板設(shè)計(jì)

VCXO CLK發(fā)生器的質(zhì)量和特性會(huì)受到晶體選擇和PCB布局的影響.在晶體選擇方面,除頻率,封裝,精度和工作溫度范圍外,對(duì)于VCXO應(yīng)用,用戶必須注意等效串聯(lián)電阻和負(fù)載電容.串聯(lián)電阻提供晶體的功耗測(cè)量.電阻值越小,振蕩器啟動(dòng)越容易.負(fù)載電容是晶體的重要參數(shù).首先,它決定了晶體的共振頻率.通常,晶體的標(biāo)記頻率意味著在將指定的負(fù)載電容與其并聯(lián)連接之后晶體的諧振頻率.大號(hào)等于規(guī)定的負(fù)載電容,但這不是將值從1/(2π√L1Ç1).因此,很明顯VCXO的調(diào)諧范圍與CL的值密切相關(guān).對(duì)于較小的負(fù)載電容值,VCXO調(diào)諧范圍限制在上側(cè);同樣,較大的電容值會(huì)降低下側(cè)的調(diào)諧范圍.加載電容的正確值取決于VCXO的特性.

例如,在MAX9485設(shè)計(jì)中,為了平衡調(diào)諧范圍,調(diào)諧曲線的中心和電路板設(shè)計(jì)的簡(jiǎn)易性,我們選擇了Ecliptek(ECX-5527-27)[2]的具有14pf負(fù)載電容的27MHz晶振.有了這樣的晶體,MAX9485可以提供±200ppm的脈沖范圍,參見圖3.應(yīng)該提到的是,晶體的拉伸范圍也隨包裝而變化.通常,金屬罐裝封裝具有比表面安裝器件(SMD)更大的拉動(dòng)范圍.然而,最近DAISHINKUCorp[5]制造了一種新的SMD晶體,可提供與金屬罐裝晶體相似的拉伸范圍.我們測(cè)試了SMD晶振(DSX530GA),發(fā)現(xiàn)兩個(gè)4pf并聯(lián)電容的調(diào)諧范圍約為±200ppm,見圖4.

圖4

測(cè)量輸出CLK抖動(dòng)的設(shè)置

對(duì)于石英晶體振蕩器,抖動(dòng)是一項(xiàng)重要的性能測(cè)量.有兩種最常用的抖動(dòng)定義:周期抖動(dòng)和周期間抖動(dòng),見圖5細(xì)節(jié).為了測(cè)量抖動(dòng),我們可以使用高速數(shù)字采樣示波器對(duì)大量數(shù)據(jù)進(jìn)行采樣,并根據(jù)定義計(jì)算抖動(dòng).Tektronix(TDS7254)或Lecroy(Wavepro960)的示波器使用配備的軟件提供這些測(cè)量.我們還可以使用高速數(shù)字示波器來測(cè)量時(shí)域中的周期抖動(dòng)[3].圖5顯示了設(shè)置.通過時(shí)域方法,我們無法測(cè)量周期到周期的抖動(dòng).但是,如果每個(gè)周期的抖動(dòng)噪聲是獨(dú)立且相同分布的,則周期間抖動(dòng)是周期抖動(dòng)的1.414倍.MAX9485可根據(jù)不同的音頻采樣頻率和頻率比例因子產(chǎn)生21種不同的輸出頻率.我們使用了圖6中所示的設(shè)置測(cè)量所有可能的輸出CLK頻率的周期抖動(dòng).表1顯示了測(cè)量結(jié)果.

圖5.輸出抖動(dòng)測(cè)量.

表1.周期抖動(dòng)與輸出頻率的關(guān)系

| F OUT | 縮放因子 | FS | Jp(RMS) | |

| (MHz) | 千赫 | (PS) | UI | |

| 73.728 | 768 | 96 | 21 | 0.00155 |

| 67.7376 | 768 | 88.2 | 23.2 | 0.00157 |

| 49.152 | 768 | 64 | 42.6 | 0.00209 |

| 36.864 | 768 | 48 | 40 | 0.00147 |

| 36.864 | 384 | 96 | 37 | 0.00136 |

| 33.8688 | 768 | 44.1 | 44 | 0.00149 |

| 33.8688 | 384 | 88.2 | 41.3 | 0.00140 |

| 24.5760 | 768 | 32 | 66 | 0.00162 |

| 24.5760 | 384 | 64 | 92 | 0.00226 |

| 24.5760 | 256 | 96 | 50 | 0.00123 |

| 22.5792 | 256 | 88.2 | 55.1 | 0.00124 |

| 18.4320 | 384 | 48 | 59 | 0.00109 |

| 16.9344 | 384 | 44.1 | 69 | 0.00117 |

| 16.3840 | 256 | 64 | 134 | 0.00220 |

| 12.2880 | 256 | 48 | 84.8 | 0.00104 |

| 12.2880 | 384 | 32 | 170 | 0.00209 |

| 11.2896 | 256 | 44.1 | 100 | 0.00113 |

| 9.126 | 768 | 12 | 106 | 0.00097 |

| 8.1920 | 256 | 32 | 250 | 0.00205 |

| 4.608 | 384 | 12 | 198 | 0.00091 |

| 3.072 | 256 | 12 | 324 | 0.00100 |

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2024-03-08]IQD晶體尺寸縮小的設(shè)計(jì)效果LFXT...

- [2024-03-07]Golledge衛(wèi)星通信中的頻率控制產(chǎn)...

- [2024-03-07]Golledge工業(yè)自動(dòng)化和控制系統(tǒng)中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩(wěn)定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統(tǒng)關(guān)鍵應(yīng)用程序設(shè)計(jì)和制...

- [2024-01-06]溫補(bǔ)補(bǔ)償振蕩器的原理及特點(diǎn)

業(yè)務(wù)經(jīng)理

業(yè)務(wù)經(jīng)理 客服經(jīng)理

客服經(jīng)理